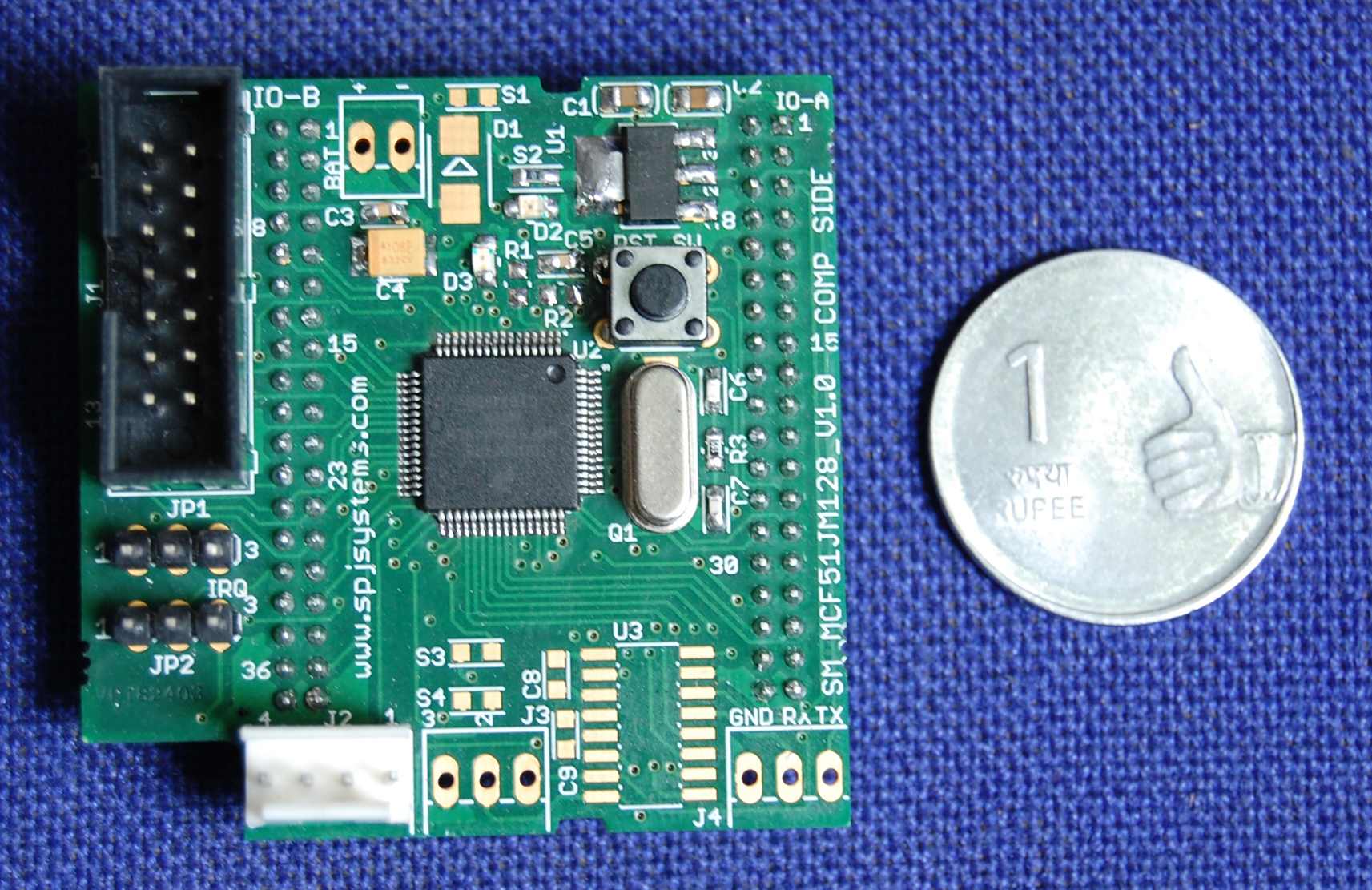

MCF51JM128 Freescale

The MCF51JM128 is a member of the ColdFire family of 32-bit reduced instruction set computing (RISC) microprocessors. It is a series is based on the V1 ColdFire core and operates at processor core speeds up to 50.33 MHz. As part of Freescale's Controller Continuum, it is an ideal upgrade for designs based on the MC9S08JM60 series of 8-bit microcontrollers.

The MCF51JM128 features the following functional units:

- V1 ColdFire core with background debug module

- Single-wire Background debug interface

- 4 Program Counters plus two address (optional data) breakpoint registers with programmable 1- or 2-level triggerresponse

- 64-entry processor status and debug data trace buffer with programmable start/stop conditions

- Up to 128 KB of flash memory

- Up to 16 KB of static RAM (SRAM)

- Multipurpose clock generator (MCG)

- Dual-role Universal Serial Bus On-The-Go device (USBOTG)

- Analog comparators (ACMP)

- Analog-to-digital converter (ADC) with up to 12 channels

- Two Inter-integrated circuit (IIC) modules

- Two serial peripheral interfaces (SPI)

- Two serial peripheral interfaces with full-duplex or single-wire bidirectional

- Double-buffered transmit and receive

- Programmable transmit bit rate, phase, polarity, and Slave Select output

- MSB-first or LSB-first shifting

- Two serial communications interfaces (SCI)

- Carrier modulation timer (CMT)

- Eight-channel timer/pulse-width modulators (TPM)

- Real-time counter (RTC)

- 66 general-purpose input/output (GPIO) modules plus Interrupt request input

- Eight keyboard interrupts (KBI)

- 16-bit Rapid GPIO

- Oscillator (XOSC) - Loop-control Pierce oscillator; crystal or ceramic resonator range of 31.25 kHz to 38.4 kHz or 1 MHz to 16 MHz

- FLL/PLL controlled by internal or external reference

- Trimmable internal reference allows 0.2% resolution and 2% deviation

- Power-saving modes

- Two low-power stop plus wait modes

- Peripheral clock enable register can disable clocks to unused modules, thereby reducing currents; this behavior

- allows clocks to remain enabled to specific perhipherals in Stop3 mode

- Very lower power real-time counter for use in run, wait, and stop modes with internal and external clock sources